Paulo Ricardo Lisboa de Almeida

Por que as instruções a seguir geram um hazard de controle?

| endereço | instrução     |  |  |  |

|----------|---------------|--|--|--|

| 40       | beq x1,x0,16  |  |  |  |

| 44       | and x12,x2,x5 |  |  |  |

| 48       | or x13,x6,x2  |  |  |  |

| 52       | add x14,x2,x2 |  |  |  |

|          |               |  |  |  |

| 72       | lw x4,100(x7) |  |  |  |

|          |               |  |  |  |

|          |               |  |  |  |

Por que as instruções a seguir geram um hazard de controle?

```

endereço instrução

40 beq x1,x0,16 #Não sabemos qual será a proxima instrução

44 and x12,x2,x5 #Essa?

48 or x13,x6,x2

52 add x14,x2,x2

...

72 lw x4,100(x7)#Ou essa?

...

```

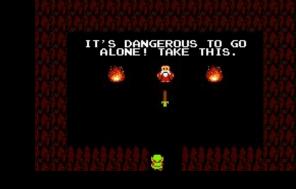

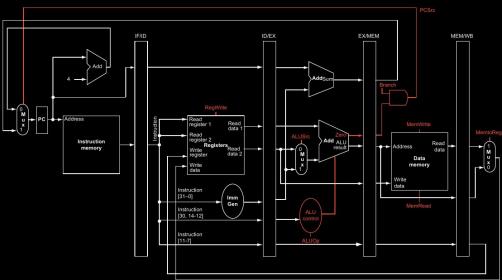

Exemplo

# Exemplo

? beq x1, x0, 16

Podemos fazer um pipeline stall.

Inserir bolhas (nops).

Podemos fazer um pipeline stall.

Inserir bolhas (nops).

Ineficiente.

Outras soluções?

Podemos fazer um pipeline stall.

Inserir bolhas (nops).

Ineficiente.

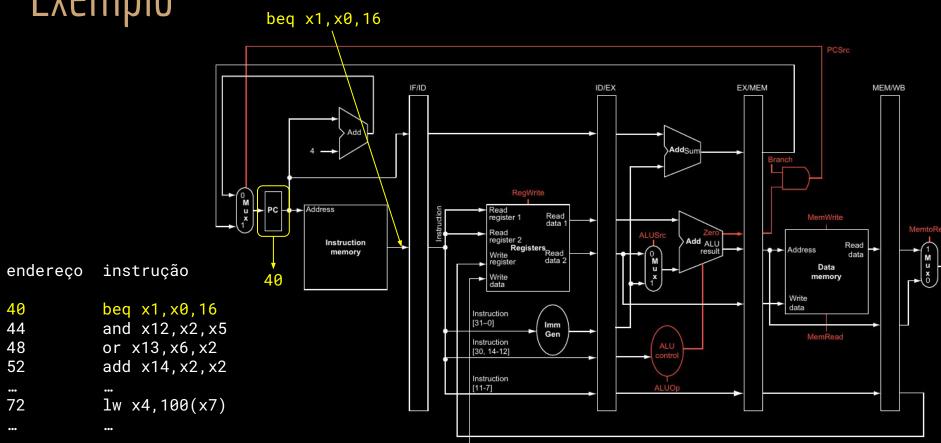

Vamos partir de uma solução simples:

Partir do princípio que o desvio nunca é tomado.

Sempre carregar e iniciar a próxima instrução.

Se estivermos errados, desfazemos tudo e continuamos a partir do endereço correto.

Podemos assumir que acertamos cerca de 50% das vezes.

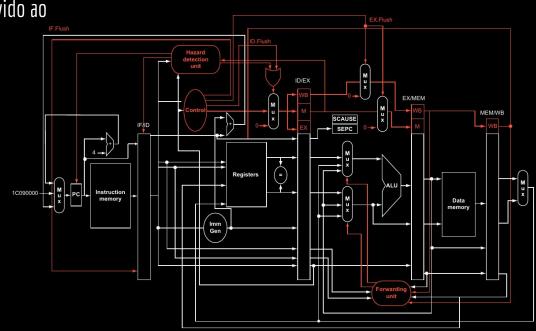

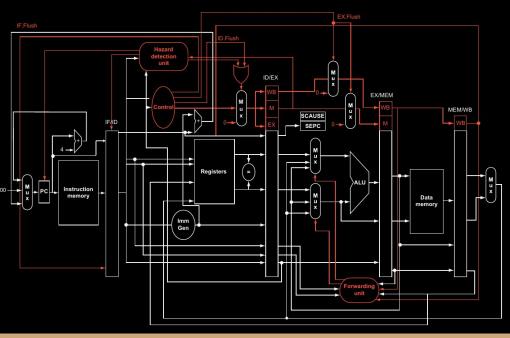

#### Assumir que o desvio nunca é tomado

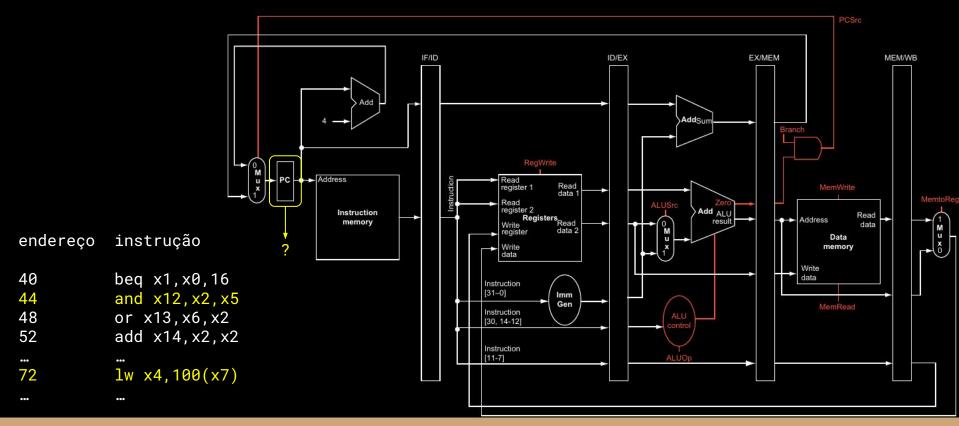

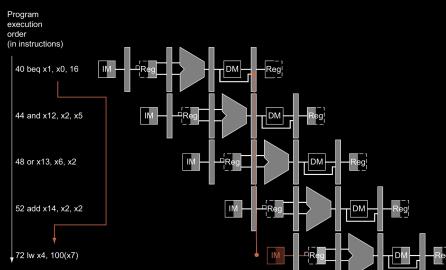

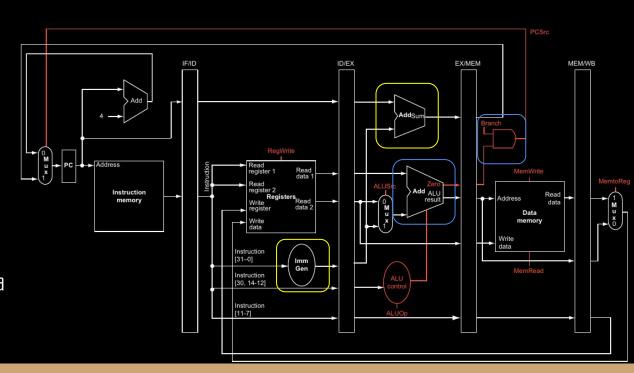

Caso a previsão esteja incorreta, 3 instruções precisam ser descartadas.

Uma no estágio EX, uma no ID, e uma no IF.

#### Como descartar?

CC8

Time (in clock cycles)

CC 2

Caso a previsão esteja incorreta, 3 instruções precisam ser descartadas. Uma no estágio EX, uma no ID, e uma no IF.

Como descartar?

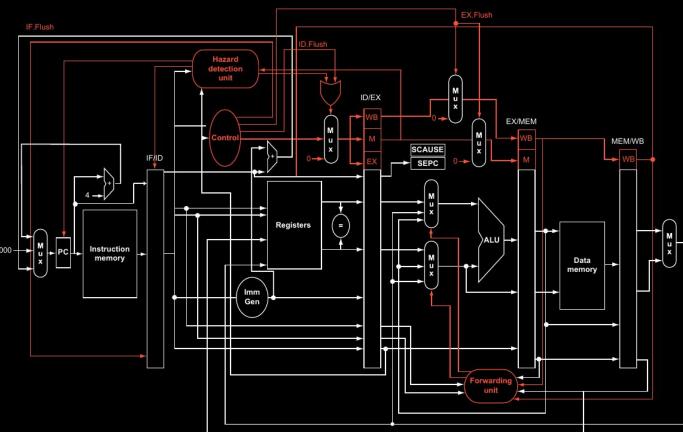

Zerar sinais de controle para instruções nesses estágios.

De maneira similar à detecção de hazards de dados, colocar zeros nos sinais de controle dessas instruções para que nada seja alterado. Se tornam nops.

Precisamos ainda injetar um nop no lugar da instrução que está no primeiro estágio. Trocar seu opcode.

#### nops

No caso de "previsão incorreta", estamos descartando três instruções.

Três nops são processados.

Três ciclos de clock inutilizados.

Por enquanto assumimos que o resultado do branch só está pronto a partir dos registradores EX/MEM.

Se conseguirmos calcular os resultados antes, podemos reduzir o custo de uma previsão incorreta.

Chegamos a conclusão se o desvio está incorreto antes.

Se a previsão está incorreta, menos trabalho é jogado fora.

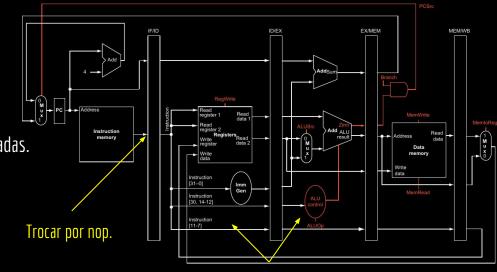

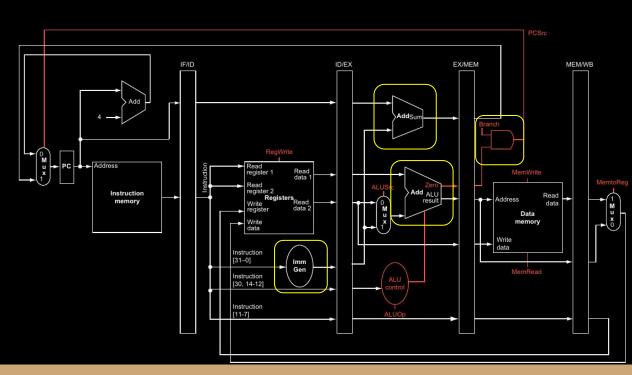

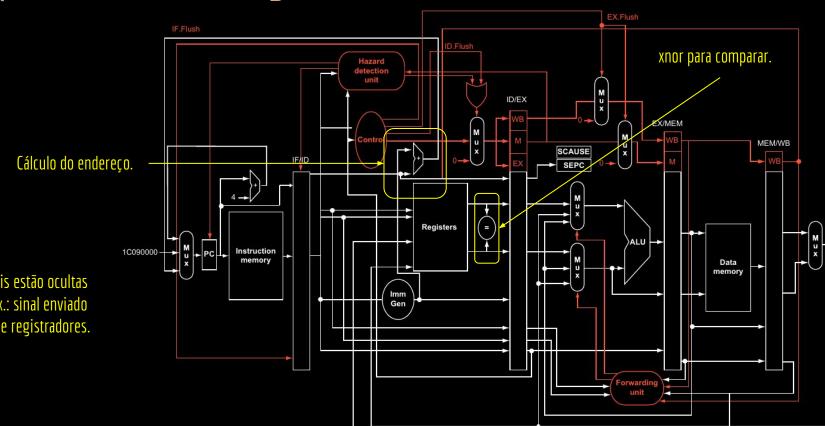

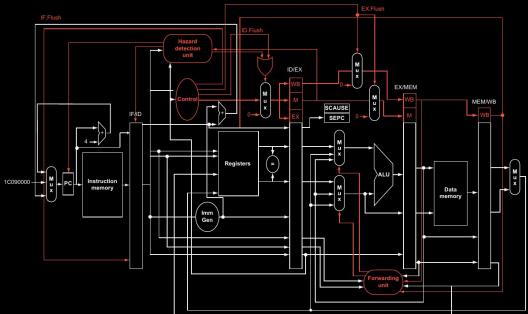

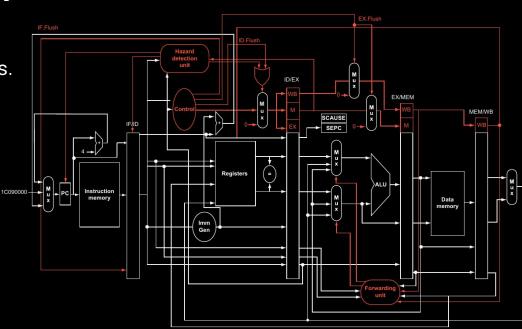

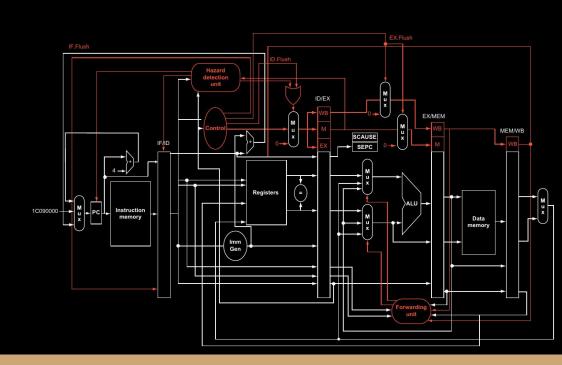

Em destaque estão algumas das principais estruturas envolvidas em um branch.

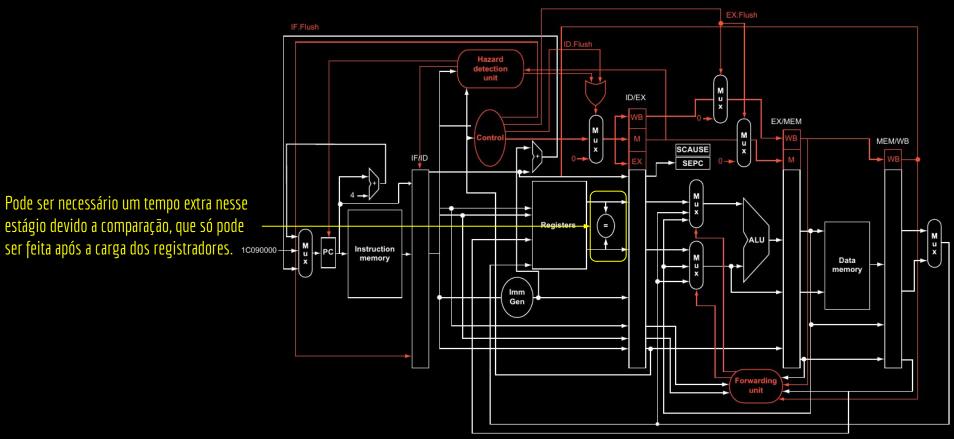

Como realizar tudo no estágio ID?

Calcular o imediato do salto através do imediato somado ao PC.

Informações já disponíveis no estágio ID.

Basta mover os componentes responsáveis. Não há atraso extra.

Esses valores podem ser calculados em paralelo, enquanto o banco de registradores busca pelas informações e a unidade de controle gera os sinais.

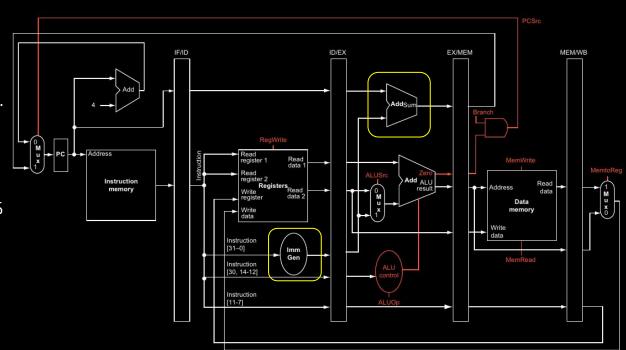

#### A comparação é mais complicada.

Quem está fazendo é a ALU.

Podemos criar um circuito **rápido especialista** para a comparação.

Como comparar?

#### A comparação é mais complicada.

Quem está fazendo é a ALU.

Podemos criar um circuito **rápido especialista** para a comparação.

Um xnor entre duas palavras retorna 1 se elas forem iguais.

REG1 xnor REG2.

Precisamos colocar esse circuito após a carga dos dados dos registradores.

Boa parte dos sinais estão ocultas para simplificar. Ex.: sinal enviado pelo comparador de registradores.

Quais são os custos envolvidos nesta alteração?

R\$, tempo, complexidade, ...

Trazer a comparação para um estágio anterior adicionando mais hardware como feito **é sempre** uma boa ideia?

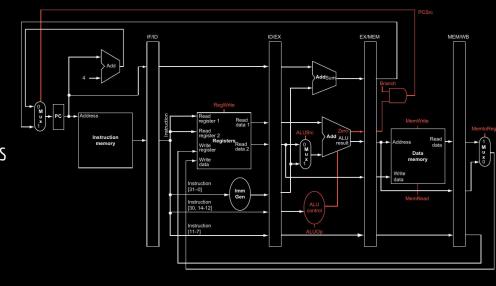

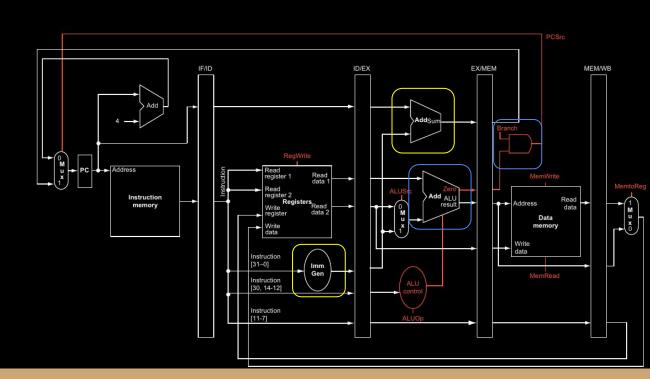

Redução do custo de uma previsão incorreta.

Agora no máximo uma bolha (nop) é necessária devido ao

hazard de controle.

Redução do custo de uma previsão incorreta.

Agora no máximo uma bolha (nop) é necessária devido ao

hazard de controle.

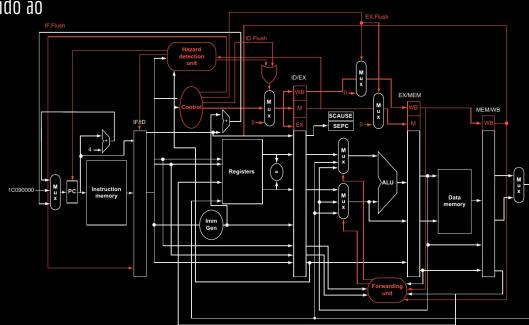

#### Criamos novos hazards de dados!

Por quê? Onde? Como?

Para cada problema resolvido,

criamos vários novos!

Operandos do **beq** podem estar sendo calculados em algum estágio do pipeline. Lógica extra de forwarding para o estágio ID.

Operandos do **beq** podem estar sendo calculados em algum estágio do pipeline. Lógica extra de forwarding para o estágio ID.

Detectar hazards de dados sem solução, para inserir nops.

Ex.: Um beq que depende de um 1w anterior.

Mais complexidade na unidade de detecção de hazards.

Operandos do **beq** podem estar sendo calculados em algum estágio do pipeline. Lógica extra de forwarding para o estágio ID.

Detectar hazards de dados sem solução, para inserir nops.

Ex.: Um beq que depende de um 1w anterior.

Mais complexidade na unidade de detecção de hazards.

Vamos nos contentar em saber que esses novos problemas existem, mas não vamos colocar o hardware para resolver.

# Pipeline.

O custo de uma previsão incorreta pode ser excessivamente alto em uma CPU de **pipeline profundo** Várias instruções podem ser descartadas!

| Microproce     | essador  | Ano  | Clock     | Estágios<br>Pipeline | Tamanho<br>Despacho | Fora de ordem? | CPUs por<br>Chip | Potência |

|----------------|----------|------|-----------|----------------------|---------------------|----------------|------------------|----------|

| 486            |          | 1989 | 0,025 GHz | 5                    | 1                   | Nāo            | 1                | 5 W      |

| Pentium        |          | 1993 | 0,066 GHz | 5                    | 2                   | Nāo            | 1                | 10 W     |

| Pentium Pro    |          | 1997 | 0,2 GHz   | 10                   | 3                   | Sim            | 1                | 29 W     |

| Pentium 4 W    | llamette | 2001 | 2 GHz     | 22                   | 3                   | Sim            | 1                | 75 W     |

| Pentium 4 Pr   | escott   | 2004 | 3,6 GHz   | 31                   | 3                   | Sim            | 1                | 103 W    |

| Intel Core     |          | 2006 | 3 GHz     | 14                   | 4                   | Sim            | 2                | 75 W     |

| Core i7 Nehal  | em       | 2008 | 3,6 GHz   | 14                   | 4                   | Sim            | 2-4              | 87 W     |

| Core Westme    | re       | 2010 | 3,73 GHz  | 14                   | 4                   | Sim            | 6                | 130 W    |

| Core i7 Ivy Br | idge     | 2012 | 3,4 GHz   | 14                   | 4                   | Sim            | 6                | 130 W    |

| Core Broadwe   | 2        | 2014 | 3,7 GHz   | 14                   | 4                   | Sim            | 10               | 140 W    |

| Core i9 Skyla  | ке       | 2016 | 3,1 GHz   | 14                   | 4                   | Sim            | 14               | 165 W    |

| Intel Ice Lake |          | 2018 | 4,2 GHz   | 14                   | 4                   | Sim            | 16               | 185 W    |

| Intel Raptor ( | ove      | 2022 | 6.2 GHz   | 12                   | -                   | Sim            | 24               | -        |

| Intel Lion Cov | re       | 2024 | -         | 10                   | -                   | Sim            | -                | -        |

# Pipeline.

O custo de uma previsão incorreta pode ser excessivamente alto em uma CPU de **pipeline profund**.

Várias instruções podem ser descartadas!

Um pipeline profundo é ideal se conseguimos mantê-lo cheio.

Mas é complexo, e stalls custam caro. Difícil manter o pipeline sempre cheio.

|    | Microprocessador     | Ano  | Clock     | Estágios<br>Pipeline | Tamanho<br>Despacho | Fora de ordem? | CPUs por<br>Chip | Potência |

|----|----------------------|------|-----------|----------------------|---------------------|----------------|------------------|----------|

|    | 486                  | 1989 | 0,025 GHz | 5                    | 1                   | Nāo            | 1                | 5 W      |

|    | Pentium              | 1993 | 0,066 GHz | 5                    | 2                   | Nāo            | 1                | 10 W     |

| 0. | Pentium Pro          | 1997 | 0,2 GHz   | 10                   | 3                   | Sim            | 1                | 29 W     |

| U. | Pentium 4 Willamette | 2001 | 2 GHz     | 22                   | 3                   | Sim            | 1                | 75 W     |

|    | Pentium 4 Prescott   | 2004 | 3,6 GHz   | 31                   | 3                   | Sim            | 1                | 103 W    |

| 0  | Intel Core           | 2006 | 3 GHz     | 14                   | 4                   | Sim            | 2                | 75 W     |

|    | Core i7 Nehalem      | 2008 | 3,6 GHz   | 14                   | 4                   | Sim            | 2-4              | 87 W     |

|    | Core Westmere        | 2010 | 3,73 GHz  | 14                   | 4                   | Sim            | 6                | 130 W    |

|    | Core i7 Ivy Bridge   | 2012 | 3,4 GHz   | 14                   | 4                   | Sim            | 6                | 130 W    |

|    | Core Broadwell       | 2014 | 3,7 GHz   | 14                   | 4                   | Sim            | 10               | 140 W    |

|    | Core i9 Skylake      | 2016 | 3,1 GHz   | 14                   | 4                   | Sim            | 14               | 165 W    |

|    | Intel Ice Lake       | 2018 | 4,2 GHz   | 14                   | 4                   | Sim            | 16               | 185 W    |

|    | Intel Raptor Cove    | 2022 | 6.2 GHz   | 12                   | -                   | Sim            | 24               |          |

|    | Intel Lion Cove      | 2024 | _         | 10                   | -                   | Sim            | -                | _        |

# Melhorando a previsão

Algumas técnicas podem ser implementadas para aumentar a acurácia da previsão.

- Buffers de previsão de desvios.

- Delayed Slots.

- Preditores de correlação.

- Preditor de torneio.

- ..

# Melhorando a previsão

Algumas técnicas podem ser implementadas para aumentar a acurácia da previsão.

- Buffers de previsão de desvios.

- Delayed Slots.

- Preditores de correlação.

- Preditor de torneio.

- ..

Podem ser instalados no **estágio IF** do pipeline.

#### Exercícios

- 1. Releia os slides, analisando cada ponto de forma detalhada.

- 2. Utilizando portas lógicas, monte o circuito que faz a comparação entre os sinais dos registradores.

- 3. Quanto ao buffer de previsão de desvios, quais informações precisamos realmente manter em uma memória? Podemos armazenar somente o bit dizendo se o salto foi realizado ou não (segunda coluna veja em aulas passadas) e não armazenar o endereço da entrada no buffer (primeira coluna)?

# Referências

Patterson, Hennessy.

Computer Organization and

Design RISC-V Edition: The

Hardware Software

Interface. 2020.

Patterson, Hennessy. Computer Organization and Design MIPS Edition: The Hardware/Software Interface. 2020.

Stallings, W. Organização de Arquitetura de Computadores. 10a Ed. 2016.

Hennessy, Patterson. Arquitetura de Computadores: uma abordagem quantitativa. 2019.

# Licença

Esta obra está licenciada com uma Licença Creative Commons Atribuição 4.0 Internacional.